Understanding FinFETs: The Complex World of Advanced Transistors

A basic introduction to FinFETs, comparing them to traditional transistors and discussing the complex issues and potential benefits of FinFET technology.

00:00:01 This video provides a basic introduction to FinFETs, comparing them to traditional transistors and discussing the complex issues and potential benefits of FinFET technology. It also highlights the move from bulk to FinFETs as a solution to performance and variability problems in semiconductor technology.

📚 FinFETs are a new type of device that attracted a lot of attention.

⚙️ FinFET technology has complex issues associated with it, such as processing variability and time-dependent variability.

🔬 There is a benchmark between bulk devices and SOI-based devices to compare their differences and potential.

00:05:21 FinFETs are a vertical transistor design that present challenges in scaling and variability for SRAM. There are two types: bulk and SOI substrate. Bulk FinFETs have deeper etching for isolation, while SOI FinFETs only etch the fin. Each type has its own advantages and disadvantages.

📚 FinFETs are a type of transistor that have a vertical channel and gates around the channel, creating conceptual problems for designers.

🔧 There are two flavors of FinFETs: bulk FinFETs, adopted by major providers, and FinFETs on SOI substrate, which have better control over transistor dimensions but may have self-heating effects.

💡 FinFETs offer a more complicated operation compared to planar transistors, and their variability poses challenges for scaling SRAM in small devices.

00:10:39 FinFETs have a non-uniform charge distribution in the channel, with more charge near the corners. They have better suppression of sub-threshold leakage and offer potential for improved performance and lower leakage. However, their complex geometry and layout pose challenges.

🔑 FinFETs are a type of transistor that have a different charge distribution compared to depleted transistors.

💡 Current flow in FinFETs is non-uniform, with most of the current flowing in the middle at threshold voltage and through the corners at high gate voltage.

📈 FinFETs have better suppression swap in both transistors, resulting in lower subthreshold swap and potential advantages in terms of leakage and performance.

00:16:01 This video discusses the introduction of FinFETs, their complex geometry, and the impact of different fabrication steps on their performance.

🔑 FinFETs introduce additional capacitances due to vertical fin geometry and overgrown source and drain regions, resulting in complex capacitance variations.

🏗️ FinFET fabrication is more complex and involves vertical etching and epitaxial growth, leading to variations in fin shape and contact resistance.

🔬 Device simulation of FinFETs is challenging due to their complex geometry, including triangular or trapezoidal structures and quantum confinement effects.

⚡ Triangular FinFET geometry may have reliability issues and suboptimal performance compared to vertical FinFETs.

00:21:25 This video discusses the fabrication and performance of FinFETs compared to rectangular transistors. It explores the impact of realistic shapes on transistor performance and the sacrifice of short channel effects. The study also compares the performance of bulk and SOI transistors, finding that SOI FinFETs have higher performance and lower leakage current. The video concludes with an overview of an interesting study conducted with IBM on the impact of FinFETs.

🔑 FinFETs are difficult to fabricate uniformly and their performance is affected by variations in shape.

💡 Compared to rectangular transistors, FinFETs have lower performance by 10 to 12 percent.

🔬 A case study comparing bulk and SOI transistors showed that SOI FinFETs had higher performance and lower leakage current.

00:26:45 This video discusses the impact of process control and variability on FinFET performance and explores the optimization of SRAM design.

🔍 It is important to consider process variability and control different aspects of the device geometry in FinFET design.

📊 There is a strong correlation between statistical and process variability in FinFETs, which affects device performance.

🔬 Compact models can accurately capture process variation and help analyze the impact on circuit design, such as SRAM.

00:32:06 Monte Carlo simulation predicts performance and behavior of FinFETs. Accurate compact model tracks statistical variability and degradation for future technology. Simulation crucial for estimating impact on design and reliability.

🔑 Monte Carlo simulation can be used to predict the performance and behavior of FinFETs, allowing for more complex analysis of SRAM designs.

📊 Good compact models combined with statistical variability can show the interplay between process and statistical variability, helping to understand the impact on SRAM design.

⚙️ Simulation is crucial in predicting future technology and estimating the impact of different devices and degradation on SRAM cell designs.

You might also like...

Read more on Science & Technology

If I Started a Business Again Today, I'd Do This

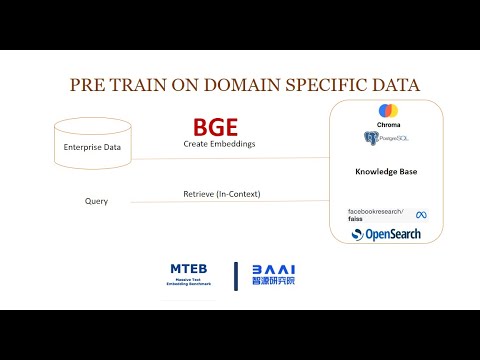

State-of-the-Art BGE embeddings for Retrieval Augmented Generation

How To Control Project Scope & Manage Your Clients | Creative Business - Effective Client Management

Israel warns Gaza to prepare for retaliation following surprise attack - BBC News

Estructura de Datos - Queue - Cola

Chatbots with RAG: LangChain Full Walkthrough